FPGA_Z80 Cyclone IV Z80 Emulation

Project Description

This project is a port of

Grant Searles Cyclone II multicomputer project

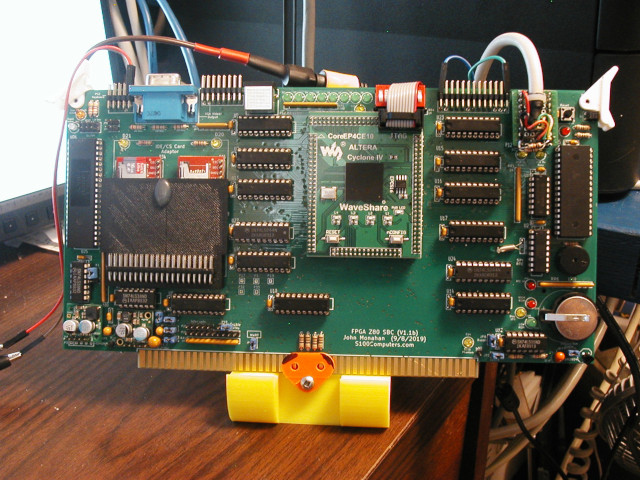

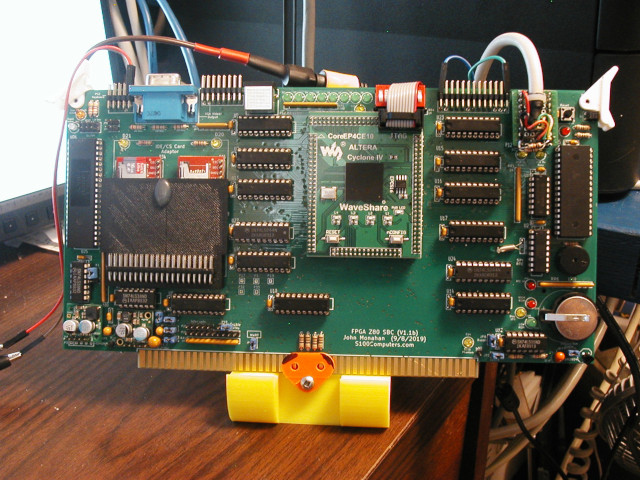

to the S100 Cyclone 4 FPGA Z80 board developed by

John Monahan.

After building Johns card, I got interested in implementing an MMU in the

FPGA so I could use banked ram in CPM3 to access all of the 512K ram on Johns card.

I found Grants project that had a very nice MMU implentation written in VHDL.

Grant had used a Cyclone II FPGA card to implement a very extensive and well designed

framework for emulating various CPU's, I/O devices and operating systems.

I considered a couple of options to explore... port the MMU to Johns code

and build a banked memory version of CPM3, or port Grants code and ideas to Johns

board and try running the images and OS options that were available with Grants design.

As it turned out, I learned a great deal porting Grants design to the FPGA_Z80 hardware.

This is still a work in progress, but I am at a point, that I wanted to share my

developments with other builders of Johns card. So far, I have implemented

- the SPI interface to the first uSD card - the hard drive emulation

- a port to read from the DIP switches

- a port to write to the 8 LED bank on the top of Johns card

- a serial UART with fifo buffer for the console

- a single bit port for driving the buzzer

- MMU using 32 16k pages that get mapped into 1 of 4 16K slots in the Z80 address space

- A memory test that tests all of the 512K ram chip using rolling page setups.

Things I would like to get working...

- spi interface to the RTC hardware ( done )

- some minimal S100 bus functionality like read/write off board IO ports

- VGA display possibly with its own Z80 to get the video buffer out of the system Z80 memory space.

- VGA attributes.. flashing, inverse video, underline/block cursor, character color

- maybe a tek 4010/4014/4016 graphics terminal emulation

- PS/2 keyboard support

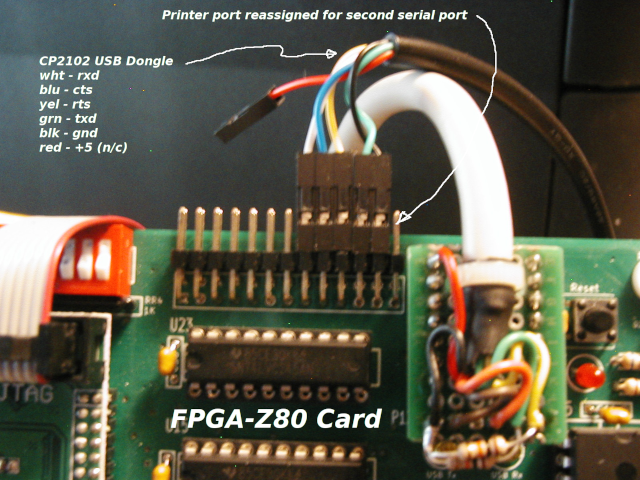

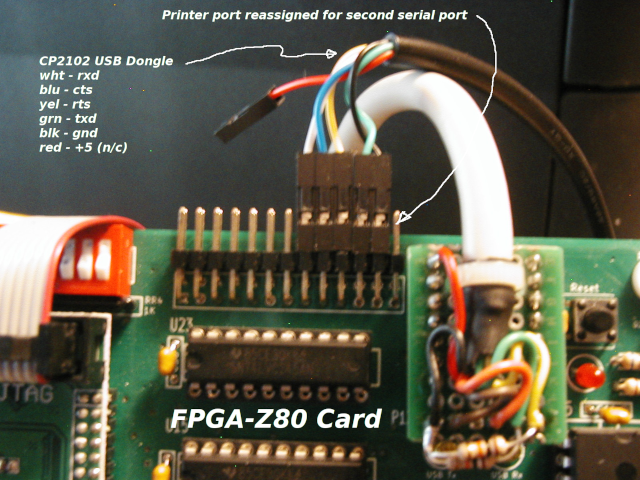

- implement printer port ( now using this port for a second serial port )

- find I/O for the second serial port (currently stubbed with no assigned I/O) (done)

- experiment with higher speed clocks

- change the disk format from 512 directory entries to 1024 entries. Impacts a lot of code in every operating system

- In the Quartus project, I would like to understand how to generate Microcomputer.sdc to eliminate all the timing constraint warnings.

Updates

UPDATE: 20 Mar 2022

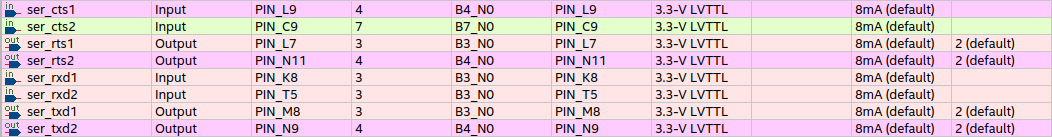

I have used 4 bits of the the printer port to provide 2 input and 2 output bits

to use for a second serial port. The serial port plugs directly onto 5 of the printer

port pins as shown in the photo below.

Second Serial Port Connections

Second Serial Port Connections

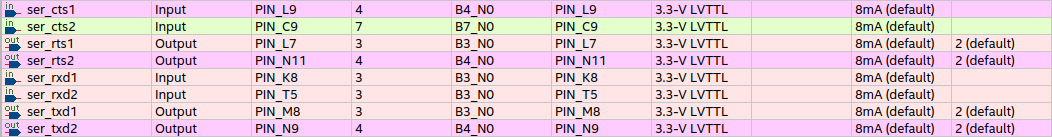

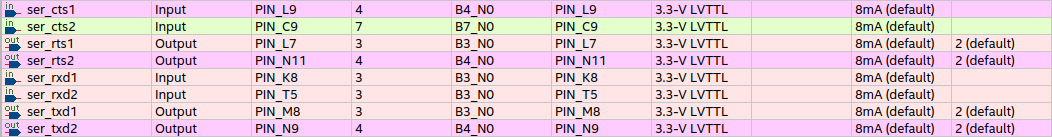

Serial Port FPGA Pin Assignments

Serial Port FPGA Pin Assignments

UPDATE 15 April 2022

I implemented a bit banged SPI port to talk with the real time clock chip

and have a routine called ds1305(.c,.com) that is used to test the RTC and also allow

setting CPM time from the RTC time.

In disk image 3, user 0 has been set up with a bunch of

useful utilities. Most of the .com files have been marked with the [sys] attribute

so they can be used from whatever user area you happen to be in.

A nice screen editor called vedit has been installed. This editor has the advantage of

being able to edit files larger than the TPA.

User area 3 has been setup with most of assembler related files and user area 4

has been setup with BDS C V1.6 C related files.

Kermit and xmodem have been compiled and installed to use the second serial

port as the data highway to the linux box.

Booting CPM3

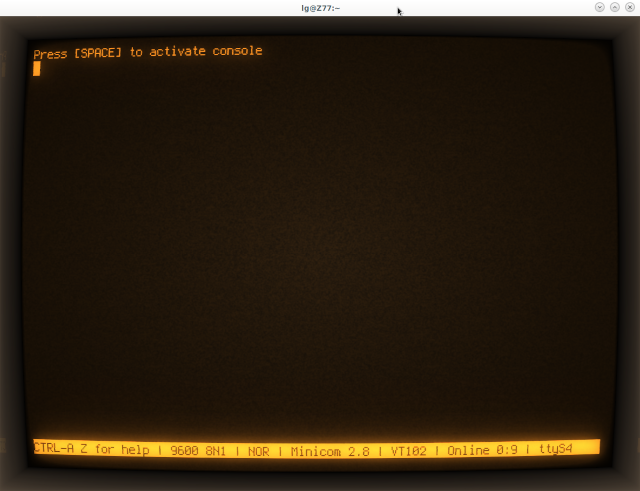

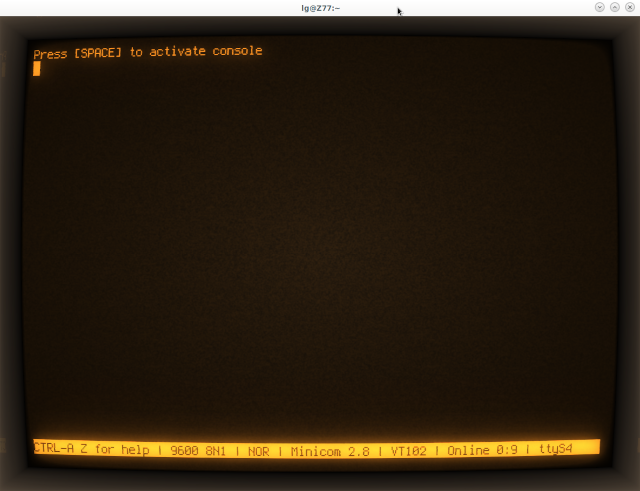

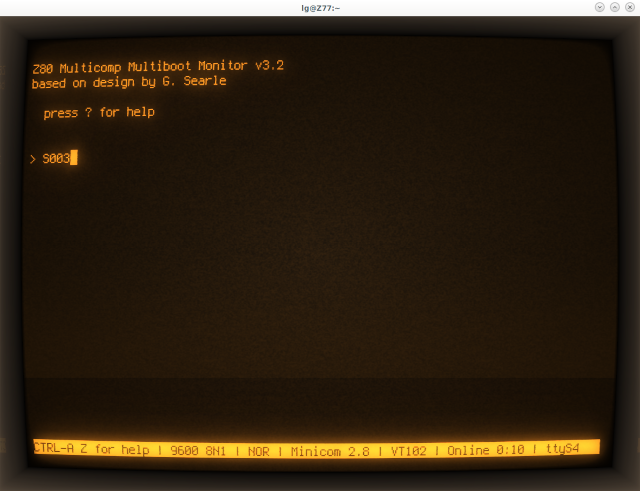

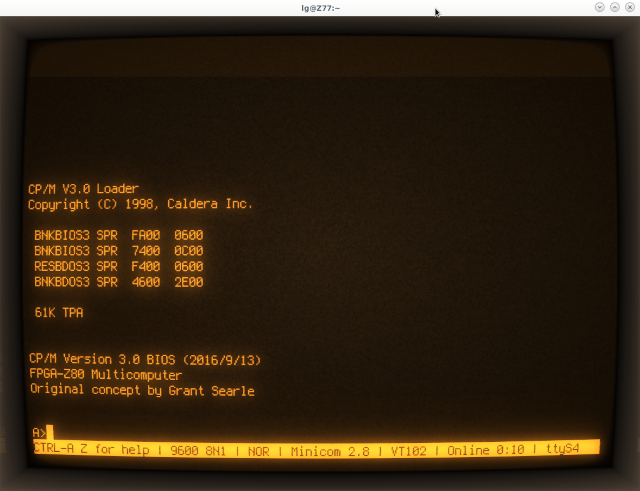

The following 3 screen shots show what you should see when booting volume 3 (CPM3 system) from a reset.

Monitor after a reset...

Monitor after a reset...

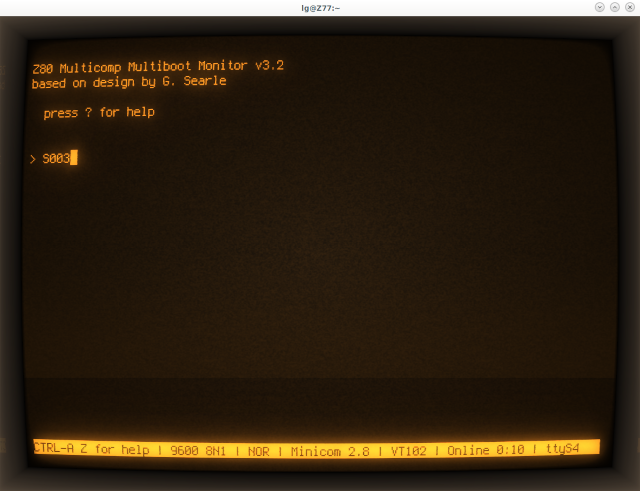

Selecting Volume 3 (CPM3) for booting...

Selecting Volume 3 (CPM3) for booting...

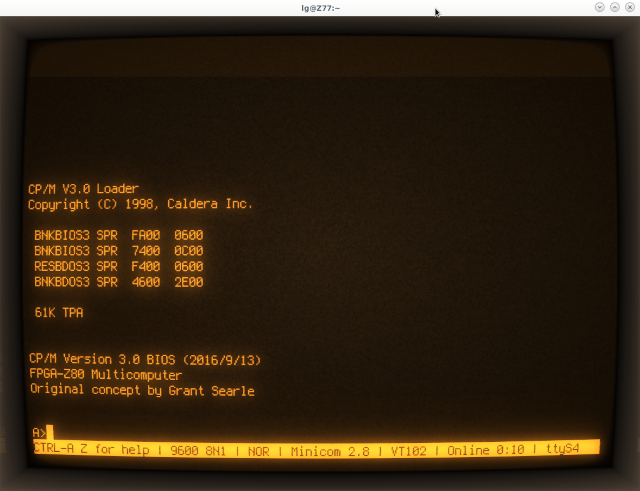

CPM3 all booted and ready for action...

CPM3 all booted and ready for action...

System Requirements

- a functioning FPGA_Z80 card from the S100Computers site.

- Intel Quartus Prime 21.1 Lite Edition installed on your PC (I use linux)

- a USB Blaster for programming the FPGA card

- the project files included below for the FPGA design

- the micro SD card image included below contaning 18 8MB disk images

To use cpmtools with Grants disk images, you will need to add the following to the file diskdefs used by cpmtools

# disk format for grant searles images

diskdef gsearle

seclen 512

tracks 512

sectrk 32

blocksize 4096

maxdir 512

skew 0

boottrk 1

os 3

end

I am working on getting some scripts set up to read and write the 18 hard disk volumes using cpmtools.

The multi-disk image used by Grant has the 1st 8MB empty, the 18 8MB volumes are sequentially

located one after the other. By using dd, you can unpack the volumes, use cpmtools on them and then reassemble the

monolithic image using dd again. Contact me for progress on this front. I got as far as building a custom

CPM3 volume and having it boot.

Source Code

compressed uSD card image - System18.img.zip (10MB)

unzip, copy to SD card with "sudo dd if=System18.img of=/dev/sdd bs=512 count=312000" where you are sure your uSD card is mounted on /dev/sdd!!!.

FPGA Project files - fpga-multicomp2022apr15.zip (783kB)

Unzip into your Quartus project directory. Open 14-Multicomp/Microcomputer_TTY/Microcomputer.qpf in Quartus.

FPGA programming image - Microcomputer.sof(358.7kB)

(Generated by Quartus for loading into fpga by USB Blaster dongle.)